## Master in Electronic Engineering

Implementation of the Parallel Redundancy Protocol (PRP) with encryption of frames using the Advanced Encryption Standard (AES)

Marco Andrés Ortiz Niño

Bogotá, D.C., 13-01-2021

Implementation of the Parallel Redundancy Protocol (PRP) with encryption of frames using the Advanced Encryption Standard (AES)

Thesis work to obtain a master's degree in Electronic Engineering, with an emphasis on Telecommunications.

Supervisor: Eng. Hernán Paz Pengos. PhD Co-Supervisor: Eng. Javier Evandro Soto Vargas. PhD.

Implementation of the Parallel Redundancy Protocol (PRP) with encryption of frames using the Advanced Encryption Standard (AES)

Jury:

Bogotá, D.C., 13-01-2021

The Master Thesis, Implementation of the Parallel Redundancy Protocol (PRP) with encryption of frames using the Advanced Encryption Standard (AES), presented by Marco Andrés Ortiz Niño meets the requirements established to obtain the title of Magister in Electronic Engineering with emphasis on telecommunications.

Jury:

Supervisor: Eng. Hernán Paz Penagos. PhD.

Co-Supervisor: Eng. Javier Evandro Soto Vargas. PhD.

Bogotá, D.C., 13-1-2021

#### Abstract

As industrial Networks progressively migrate their communications infrastructure to IP and Ethernet set of protocols, threads and vulnerabilities also appear to disrupt operation of infrastructure with serious repercussions. To minimize these, authentication, encryption, integrity and availability must be taken in consideration at every layer of the communication architecture. Security can be achieved by numerous algorithms and set protocols that are continuously tested and implemented to be supported on current links, networks and applications. Their implementations are performed to accomplish high throughput and reduced logic utilization depending on industry or sector requirements. Particularly, this work deals with confidentiality and availability at data link layer where Ethernet resides. Advanced Encryption Standard (AES) with Counter mode (CTR) are used for confidentiality and the Parallel Redundancy Protocol (PRP) for redundancy. These are selected due to their communication orientation, broad operation lifetime expectancy, and their direct relation to secure industrial networks for critical and non-critical infrastructures. Advanced Encryption Standard (AES)-Counter mode (CTR) logic an its Intellectual Property (IP) Cores are created using Very High Speed Integrated Circuit Hardware Description Language (VHDL) within Xilinx Vivado and tested using the Zynq7000 System on Chip (SoC)-Field Programable Gate Array (FPGA) and Kintex 7 FPGA. Parallel Redundancy Protocol (PRP) is implemented on software to govern the protocol algorithm, data encryption operation and packet framing. To test integration between these components, the embedded processor of the Zyng 7000 (ARM) and Microblaze are used. This work presents a non-pipelined AES implementation for confidentiality, its logic utilization, maximum frequency and throughput. Results for AES are also presented in simulation for 128, 192 and 256 bit-length key sizes. At implementation, the 128 bit key is used. For redundancy, on the other hand, the PRP is implemented on software, which creates the header and trailer according to International Electrotechnical Commission (IEC) specification, and, a packet format is proposed to encrypted payloads. Integration results of AES-PRP are seen as packets that were captured in between of the communication devices.

## Contents

|                                                             | pág. |

|-------------------------------------------------------------|------|

| Introduction                                                | 16   |

| 1 Literature Review                                         | 19   |

| 1.1 Industrial networks security                            | 19   |

| 1.2 Cryptography                                            | 23   |

| 1.2.1 Symmetric algorithms                                  | 24   |

| 1.2.2 AES and the Rijndael Algorithm                        | 26   |

| 1.2.3 Modes of operation                                    | 28   |

| 1.3 Redundancy in communication networks                    | 30   |

| 1.3.1 The Parallel Redundancy Protocol - PRP                | 32   |

| 1.3.1.1 Link Redundancy Entity - LRE                        | 34   |

| 1.4 NetFPGA and ZedBoard                                    | 35   |

|                                                             |      |

| 2 Methodological Design of the Implementation               | 37   |

| 2.1 AES combinational and non-pipelined (sequential) design | 38   |

| 2.2 AES (sequential) integrated blocks for CTR              | 41   |

| 2.3 PRP framing and algorithm                               | 43   |

| 2.4 PRP and AES-CTR integration design                      | 46   |

| 2.5 PRP and AES-CTR integration verification                | 49   |

|                                                             |      |

| 3 Results and Analysis                                      | 51   |

| 3.1 AES results                                             | 51   |

| 3.1.1 Combinational AES IP Cores                         | 51 |

|----------------------------------------------------------|----|

| 3.1.1.1 Combinational AES IP Cores behavioral simulation | 52 |

| 3.1.1.2 Combinational AES IP Cores Timing                | 53 |

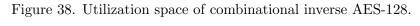

| 3.1.1.3 Combinational AES IP Cores Utilization           | 54 |

| 3.1.2 Sequential AES IP Cores                            | 56 |

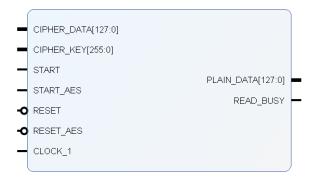

| 3.1.2.1 Sequential AES IP Cores behavioral simulation    | 56 |

| 3.1.2.2 Sequential AES IP Cores Timing                   | 59 |

| 3.1.2.3 Sequential AES IP Cores Utilization              | 60 |

| 3.1.3 AES-CTR IP Cores                                   | 62 |

| 3.1.3.1 AES-CTR IP Cores behavioral simulation           | 63 |

| 3.1.3.2 AES-CTR IP Cores Timing                          | 64 |

| 3.1.3.3 AES-CTR IP Cores utilization                     | 65 |

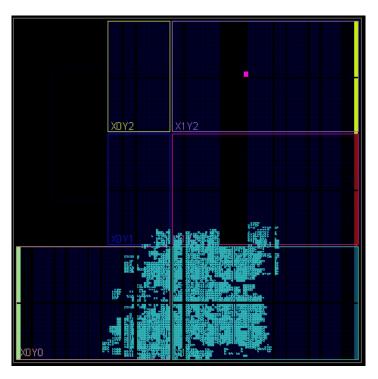

| 3.1.3.4 AES-CTR IP Core implementation                   | 68 |

| 3.1.3.5 AES IP Cores Comparative                         | 73 |

| 3.2 AES and PRP converged results                        | 75 |

| 3.3 PRP results                                          | 77 |

| 3.3.1 Packet flow                                        | 78 |

| 3.3.1.1 maximum packet size considerations               | 82 |

| 3.3.2 PRP algorithm                                      | 82 |

| 3.4 Encrypted PRP frame                                  | 82 |

| 3.5 Analysis, Discussion of Results and Future Work      | 88 |

|                                                          |    |

90

Conclusions

| Refe | erences                                                      | 94  |

|------|--------------------------------------------------------------|-----|

| Acre | onyms                                                        | 98  |

| App  | pendices                                                     | 99  |

| A.1  | Standards and guidelines for security on industrial networks | 99  |

| A.2  | VHDL AES entities                                            | 101 |

| A.3  | Combinational AES utilization report                         | 101 |

| A.4  | Sequential AES timing report                                 | 109 |

| A.5  | Sequential AES utilization reports                           | 112 |

| A.6  | AES-CTR timing reports                                       | 120 |

| A.7  | AES-CTR utilization reports                                  | 126 |

| A.8  | Verification of submitted paper.                             | 134 |

## List of Tables

|          | p                                                                                                                  | ág. |

|----------|--------------------------------------------------------------------------------------------------------------------|-----|

| Table 1  | Security requirements for Industrial Automation and Control Systems (IACS).                                        | 22  |

| Table 2  | PRP commercial devices.                                                                                            | 23  |

| Table 3  | Stream and block ciphers.                                                                                          | 25  |

| Table 4  | Key-Block-Round Combinations.                                                                                      | 27  |

| Table 5  | $\label{thm:equation:equation} \mbox{Approval Status of Symmetric Algorithms Used for Encryption and Decryption}.$ | 28  |

| Table 6  | Recommendation for key management.                                                                                 | 28  |

| Table 7  | Block cipher's Modes of operation.                                                                                 | 29  |

| Table 8  | Modes of operation Part 1 description.                                                                             | 30  |

| Table 9  | grace time per application examples.                                                                               | 31  |

| Table 10 | Examples of redundancy protocols.                                                                                  | 31  |

| Table 10 | (Continued) Examples of redundancy protocols.                                                                      | 32  |

| Table 11 | Redundancy Control Trailer (RCT) fields.                                                                           | 35  |

| Table 12 | Zedboard and NetFPGA features.                                                                                     | 35  |

| Table 12 | (Continued) Zedboard and NetFPGA features.                                                                         | 36  |

| Table 13 | Slice utilization for combinational AES.                                                                           | 55  |

| Table 14 | Slice and BRAM utilization for sequential AES-128.                                                                 | 61  |

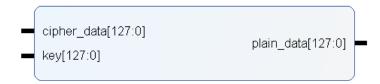

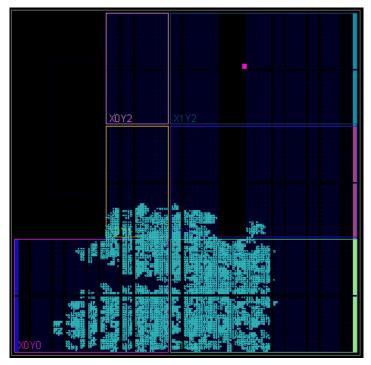

| Table 15 | IPs ports.                                                                                                         | 63  |

| Table 16 | Slice utilization for AES-CTR.                                                                                     | 68  |

| Table 17 | Slice utilization for AES IP Cores.                                                                                | 73  |

| Table 18 | Timing for AES IP Cores.                                                                                           | 73  |

| Table 19 | Comparison of AES-CTR implementation.                                                                              | 74  |

| Table 20 | Comparative of post-synthesis utilization. | 77  |

|----------|--------------------------------------------|-----|

| Table 21 | Standards and guidelines.                  | 99  |

| Table 21 | (Continued) Standards and guidelines.      | 100 |

# List of Figures

|           |                                                                            | pág. |

|-----------|----------------------------------------------------------------------------|------|

| Figure 1  | Reference Model for industrial control systems.                            | 19   |

| Figure 2  | Incidents managed by Comando Conjunto Cibernético (CCOC) and Colom-        |      |

| bian C    | Computer Emergency Readiness Team (ColCERT) in Colombia, 2015.             | 21   |

| Figure 3  | Incidents by sector in Colombia, 2015.                                     | 21   |

| Figure 4  | Cipher components.                                                         | 24   |

| Figure 5  | Stream cipher and Block cipher.                                            | 25   |

| Figure 6  | AES input block to cipher.                                                 | 26   |

| Figure 7  | AES cipher.                                                                | 27   |

| Figure 8  | PRP Redundancy Network.                                                    | 33   |

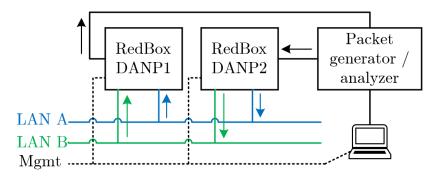

| Figure 9  | PRP with two Dual Attached Node using PRP (DANP).                          | 34   |

| Figure 10 | PRP with Redundancy Control Trailer (RCT).                                 | 35   |

| Figure 11 | Blocks of AES combinational (left), sequential (center) and sequential AES |      |

| with C    | CTR (right).                                                               | 37   |

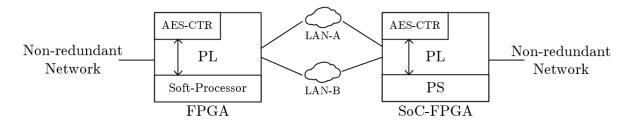

| Figure 12 | System block components.                                                   | 38   |

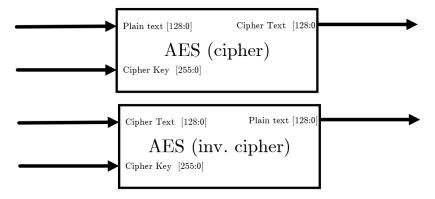

| Figure 13 | AES Cipher and inverse cipher combinational blocks.                        | 38   |

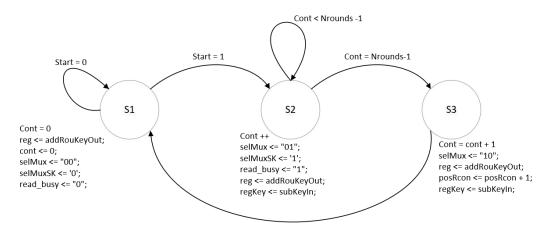

| Figure 14 | Process blocks state machine.                                              | 39   |

| Figure 15 | AES process blocks.                                                        | 40   |

| Figure 16 | Inverse AES process blocks.                                                | 40   |

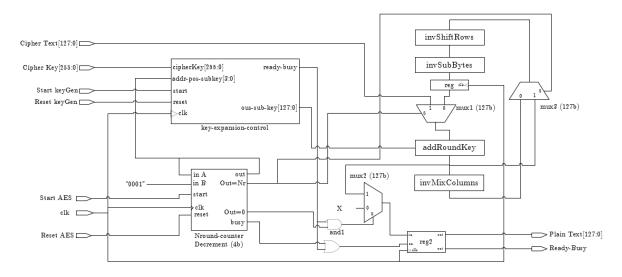

| Figure 17 | AES Cipher and inverse cipher Sequential-combinational blocks.             | 41   |

| Figure 18 | AES-CTR, Ethernet and processing system block diagram.                     | 42   |

| Figure 19 | AES-CTR, block diagram.                                                    | 43   |

| Figure 20 | Ethernet frame with PRP trailer.                                      | 43 |

|-----------|-----------------------------------------------------------------------|----|

| Figure 21 | PRP trailer details.                                                  | 44 |

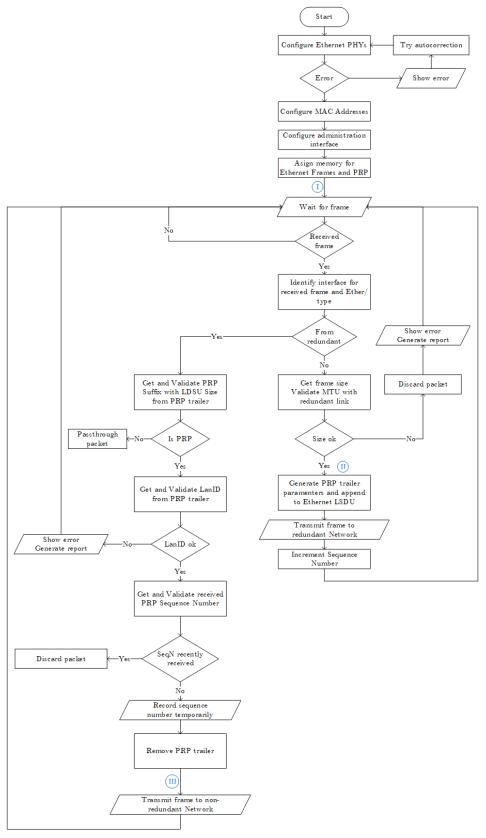

| Figure 22 | PRP Link Redundancy Entity (LRE) Flow diagram on the Processing Sys-  |    |

| tem (I    | PS).                                                                  | 45 |

| Figure 23 | Ethernet frame with encrypted Link Service Data Unit (LSDU) and plain |    |

| PRP t     | crailer.                                                              | 46 |

| Figure 24 | Ethernet with Virtual LAN (VLAN) tag and encrypted LSDU and plain     |    |

| PRP t     | crailer.                                                              | 46 |

| Figure 25 | Ethernet frame with encrypted LSDU and PRP trailer.                   | 47 |

| Figure 26 | Ethernet and VLAN tag frame with encrypted LSDU and PRP trailer.      | 47 |

| Figure 27 | PRP with AES integration flow diagram on the Processing System (PS).  | 48 |

| Figure 28 | PRP with AES-CTR Hardware integration.                                | 49 |

| Figure 29 | PRP with AES-CTR simple communication verification.                   | 50 |

| Figure 30 | PRP with AES-CTR Unit Under Test (UUT) test.                          | 50 |

| Figure 31 | IP AES cipher port diagram.                                           | 52 |

| Figure 32 | IP AES inverse cipher port diagram.                                   | 52 |

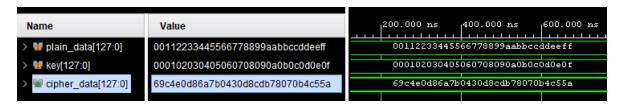

| Figure 33 | Behavioral simulation for combinational AES-128 cipher.               | 52 |

| Figure 34 | Behavioral simulation for combinational AES-128 inverse cipher.       | 53 |

| Figure 35 | Cipher worst path delay.                                              | 53 |

| Figure 36 | Inverse cipher worst path delay.                                      | 53 |

| Figure 37 | Utilization space of combinational AES-128.                           | 54 |

| Figure 38 | Utilization space of combinational inverse AES-128.                   | 55 |

| Figure 39 | AES cipher IP port diagram.                                           | 56 |

| Figure 40 | AES inverse cipher IP port diagram.                          | 56 |

|-----------|--------------------------------------------------------------|----|

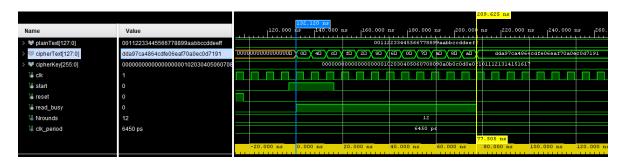

| Figure 41 | Behavioral simulation for sequential AES-128 cipher.         | 57 |

| Figure 42 | Behavioral simulation for sequential AES-192 cipher.         | 57 |

| Figure 43 | Behavioral simulation for sequential AES-256 cipher.         | 57 |

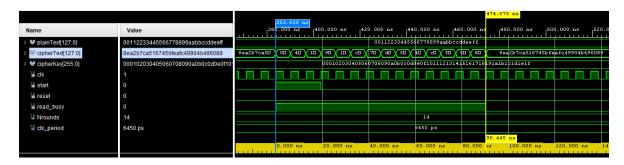

| Figure 44 | Behavioral simulation for sequential AES-128 inverse cipher. | 58 |

| Figure 45 | Behavioral simulation for sequential AES-192 inverse cipher. | 58 |

| Figure 46 | Behavioral simulation for sequential AES-256 inverse cipher. | 59 |

| Figure 47 | AES-128 cipher Synthesis Timing summary.                     | 59 |

| Figure 48 | AES-128 inverse cipher Synthesis Timing summary.             | 60 |

| Figure 49 | Utilization space of sequential AES-128.                     | 60 |

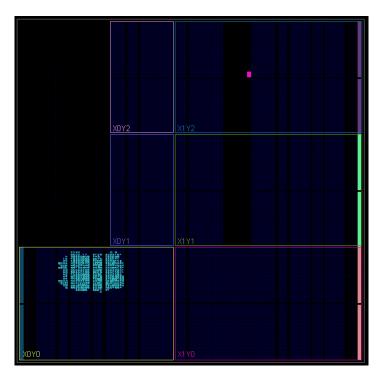

| Figure 50 | Utilization space of sequential inverse AES-128.             | 61 |

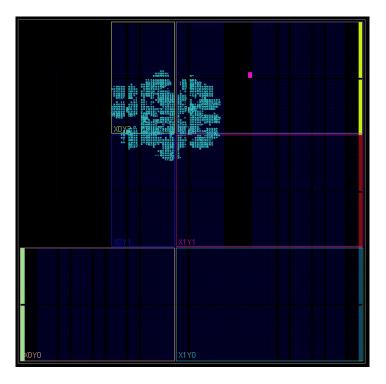

| Figure 51 | IP AES-CTR cipher port diagram and generics.                 | 62 |

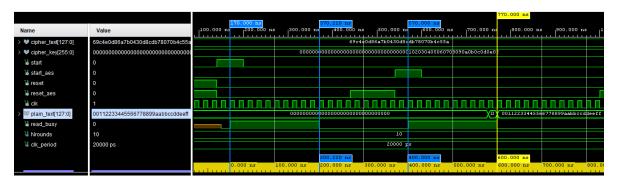

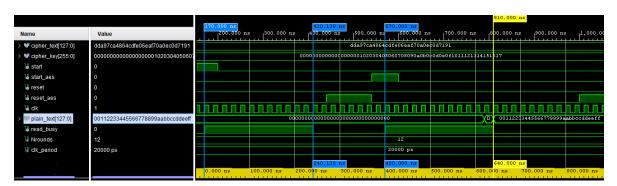

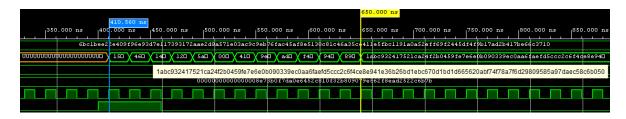

| Figure 52 | Behavioral simulation for AES-CTR-128 cipher.                | 64 |

| Figure 53 | Behavioral simulation for AES-CTR-192 cipher.                | 64 |

| Figure 54 | Behavioral simulation for AES-CTR-256 cipher.                | 64 |

| Figure 55 | Zynq 7000 AES-128-CTR Synthesis Timing Summary.              | 65 |

| Figure 56 | Kintex 7 AES-128-CTR Synthesis Timing Summary.               | 65 |

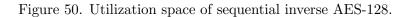

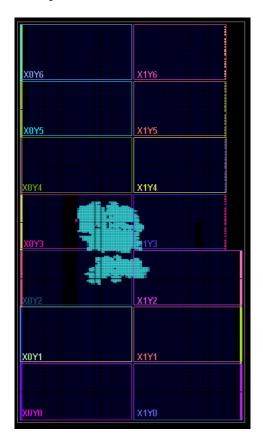

| Figure 57 | Zynq 7000 Utilization space of AES-128-CTR.                  | 66 |

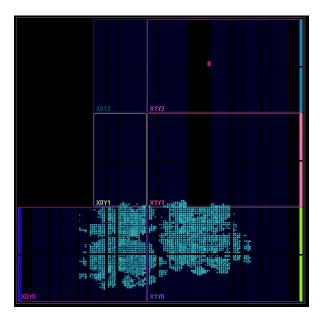

| Figure 58 | Kintex 7 Utilization space of AES-128-CTR.                   | 67 |

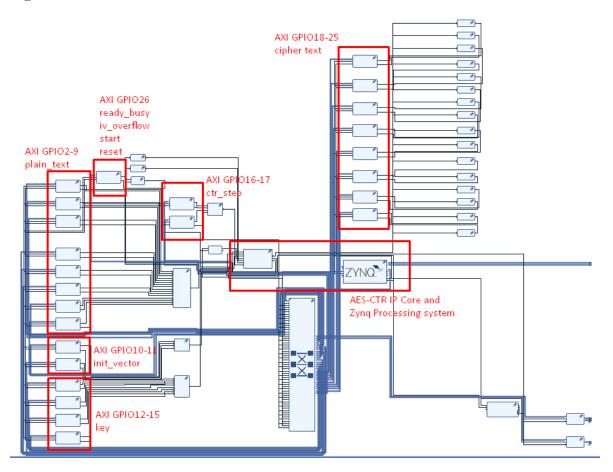

| Figure 59 | AES-CTR IP test schematic.                                   | 69 |

| Figure 60 | Synthesis, Implmentation and Bitstream generation status.    | 69 |

| Figure 61 | $gpio\_mgmt.h$ fragment.                                     | 70 |

| Figure 62 | main.c fragment with test vectors.                           | 71 |

| Figure 63 | main.c fragment with test vectors.                                      | 71  |

|-----------|-------------------------------------------------------------------------|-----|

| Figure 64 | Zedboard programmed.                                                    | 72  |

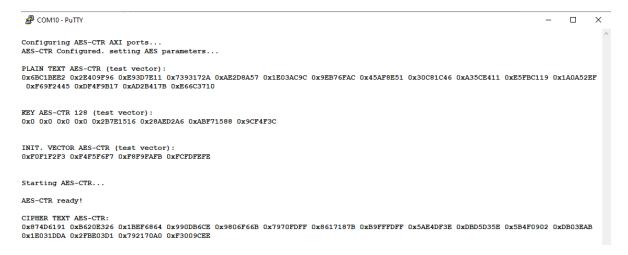

| Figure 65 | AES-CTR-128 result.                                                     | 72  |

| Figure 66 | AES-CTR, Ethernet and processing system block diagram.                  | 76  |

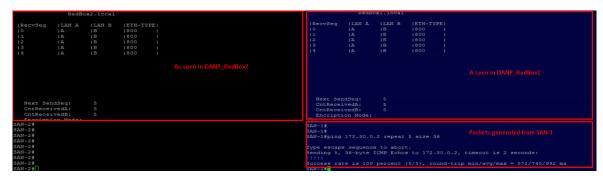

| Figure 67 | PRP logic implementation.                                               | 78  |

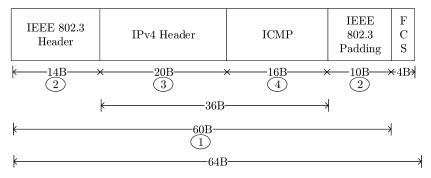

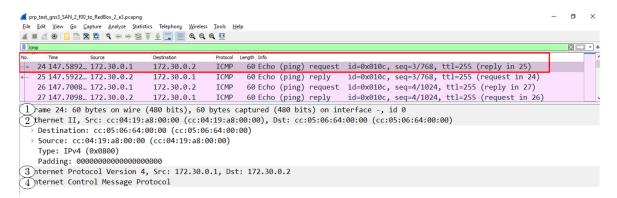

| Figure 68 | Packets in the non-redundant link with Single Attached Node (SAN)-1     | 79  |

| Figure 69 | Packet in non-redundant link with SAN-1.                                | 79  |

| Figure 70 | Packet in non-redundant link attached to SAN-1 .                        | 80  |

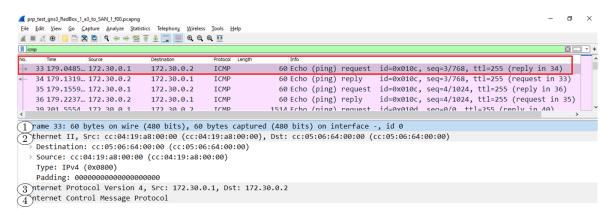

| Figure 71 | Packet format in redundant Local Area Networks (LANs).                  | 80  |

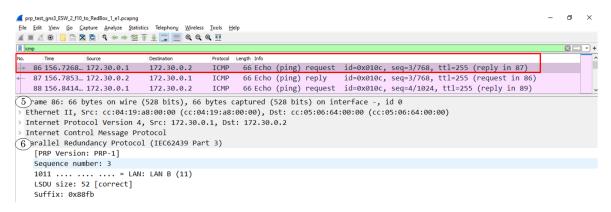

| Figure 72 | Packet in redundant LAN-A.                                              | 81  |

| Figure 73 | Packet in redundant LAN-B.                                              | 81  |

| Figure 74 | Packet in non-redundant link with SAN-2.                                | 82  |

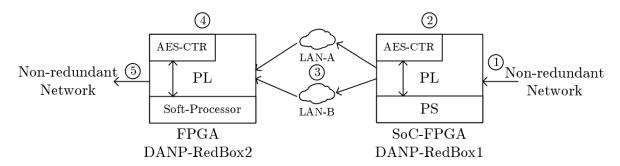

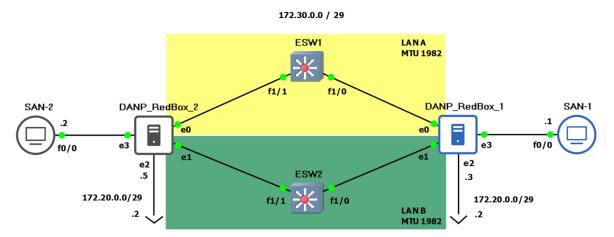

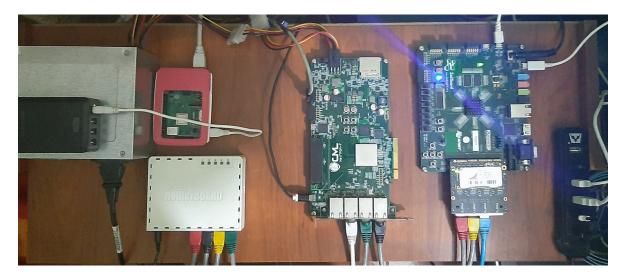

| Figure 75 | Physical components and connections for DANPs with AES-CTR.             | 83  |

| Figure 76 | Communication flow of SANs and DANPs.                                   | 84  |

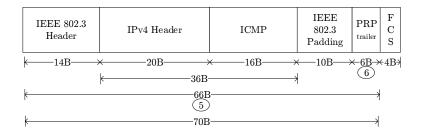

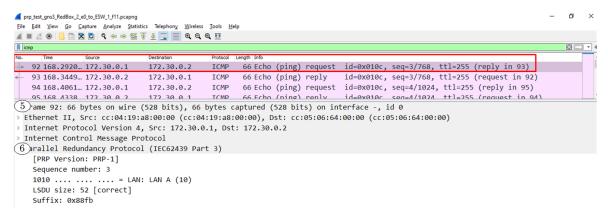

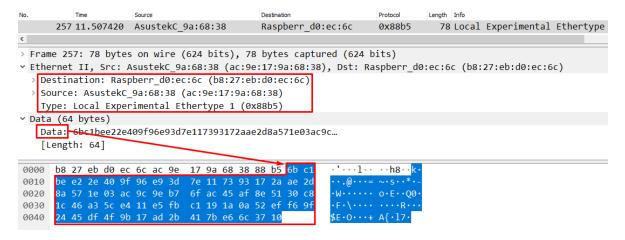

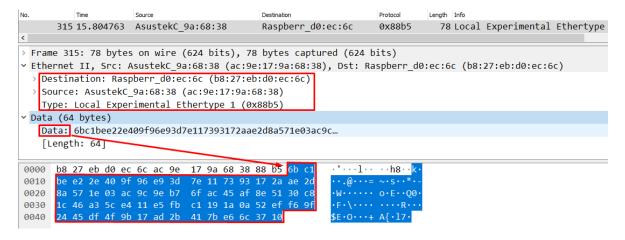

| Figure 77 | Packet sent by SAN-1 with plain data.                                   | 85  |

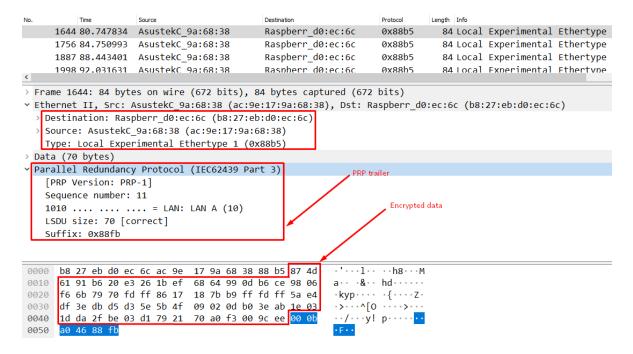

| Figure 78 | Packet sent by DANP-Redundancy Box (RedBox)-1 with cipher data and      |     |

| PRP t     | erailer on LAN-A.                                                       | 86  |

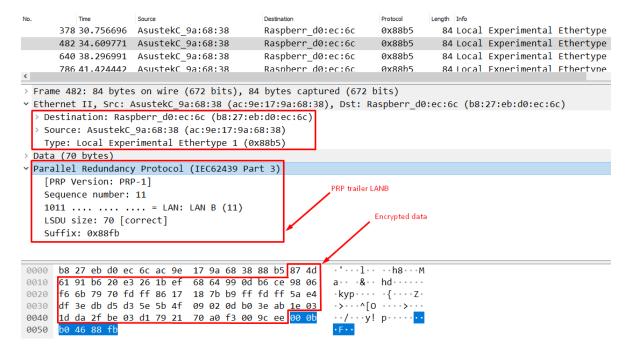

| Figure 79 | Packet sent by DANP-RedBox-1 with cipher data and PRP trailer on LAN-B. | 87  |

| Figure 80 | Packet received on SAN-2 with original plain data.                      | 88  |

| Figure 81 | Utilization combinational AES-128 report part 1.                        | 101 |

| Figure 82 | Utilization combinational AES-128 report part 2.                        | 102 |

| Figure 83 | Utilization combinational AES-128 report part 3.                        | 103 |

| Figure 84 | Utilization combinational AES-128 report part 4.                        | 104 |

| Figure 85  | Utilization combinational inverse AES-128 report part 1. | 105 |

|------------|----------------------------------------------------------|-----|

| Figure 86  | Utilization combinational inverse AES-128 report part 2. | 106 |

| Figure 87  | Utilization combinational inverse AES-128 report part 3. | 107 |

| Figure 88  | Utilization combinational inverse AES-128 report part 4. | 108 |

| Figure 89  | AES timing reports. Part 1                               | 109 |

| Figure 90  | AES timing reports. Part 2                               | 110 |

| Figure 91  | AES timing reports. Part 3                               | 111 |

| Figure 92  | AES utilization report. Part 1                           | 112 |

| Figure 93  | AES utilization report. Part 2                           | 113 |

| Figure 94  | AES utilization report. Part 3                           | 114 |

| Figure 95  | AES utilization report. Part 4                           | 115 |

| Figure 96  | inverse AES utilization report. Part 1                   | 116 |

| Figure 97  | inverse AES utilization report. Part 2                   | 117 |

| Figure 98  | inverse AES utilization report. Part 3                   | 118 |

| Figure 99  | inverse AES utilization report. Part 4                   | 119 |

| Figure 100 | AES-CTR Zynq7000 timing report. Part 1                   | 120 |

| Figure 101 | AES-CTR Zynq7000 timing report. Part 2                   | 121 |

| Figure 102 | AES-CTR Zynq7000 timing report. Part 3                   | 122 |

| Figure 103 | AES-CTR Kintex7 timing report. Part 1                    | 123 |

| Figure 104 | AES-CTR Kintex7 timing report. Part 2                    | 124 |

| Figure 105 | AES-CTR Kintex7 timing report. Part 3                    | 125 |

| Figure 106 | AES-CTR Zynq7000 utilization report. Part 1              | 126 |

| Figure 107 | AES-CTR Zynq7000 utilization report. Part 2              | 127 |

| Figure 108 AES-CTR Zynq7000 utilization report. Part 3                     | 128 |

|----------------------------------------------------------------------------|-----|

| Figure 109 AES-CTR Zynq7000 utilization report. Part 4                     | 129 |

| Figure 110 AES-CTR Kintex7 utilization report. Part 1                      | 130 |

| Figure 111 AES-CTR Kintex7 utilization report. Part2                       | 131 |

| Figure 112 AES-CTR Kintex7 utilization report. Part 3                      | 132 |

| Figure 113 AES-CTR Kintex7 utilization report. Part 4                      | 133 |

| Figure 114 Submitted paper to Computers and Electrical Engineering journal | 134 |

### Introduction

Security threats are continuously found in form of sophisticated attacks, which often are aimed to harm critical and non-critical infrastructure of both, public or private sectors. Based on these, governments and organizations develop standards and guidelines that establish requirements to prevent incidents that may affect public or private entities. Generally, requirements are achieved by defense systems, devices and protocols to enhance confidentiality, authentication and availability for data transmitted between end nodes. These data may contain classified information, supervisory and control commands among others. Several countermeasures are commonly established by means of security devices and protocols. These allow compliance of a single or set of requirements, so to improve a security scheme, protocols are combined on top of software and hardware components, allowing traditional security devices as Firewalls, Intrusion Detection Systems (IDS), Virtual Private Network (VPN) servers or antivirus software, coupling with advanced services like data loss prevention and detection of malware (Rubio, Manulis, Alcaraz, & Lopez, 2019).

In many cases, the inclusion of devices would not be advisable for many situations because: 1. Many communications devices in power industry use limited memory and processing resources, thus the overhead needed for encryption and key exchanges are not allowed (IEC 62351-1 sec. 5.6.1) as these are commonly implemented on the application, transport or network layer (upper layers); and 2. Information in a telecommunication scheme protected by cryptography, is done from source to destination point, hence, adding devices in between does not accurately secure end-to-end. Nevertheless, advanced services and devices are being adapted to industrial networks due to its migration from isolated infrastructures to interconnected systems that use protocols commonly seen in Information Technology (IT), thus, reducing operational costs and improving time response when a failure occurs, with the downside of importing IT threats which, in turn, are reported frequently with a growing trend (Rubio et al., 2019). Internet of Things (IoT) is another extension of Industrial Networks with continuous devel-

opment and innovation, modifying processes in many industries (Rost et al., 2018). Some definitions of Industrial Internet of Things (IIoT) and, mainly, an analysis framework are shown in (Boyes, Hallaq, Cunningham, & Watson, 2018). Requirements for the IIoT, as presented by (Urbina et al., 2018), are: Real-time operation, High availability, Interoperability, Data analysis and Cyber-security.

Characteristics of devices in this context can be categorized, as Boyes et al. (2018) propose: by its function, critically, easy of repair, management interface and relationship between devices, sensor and actuators. Thus, to fulfill these requirements and characteristics within industrial networks, a versatile and re-configurable approach can be made by means of FPGAs and FPGA-SoCs, as these have transformed to be a fundamental solution for development that requires high availability, high processing, real-time conditions, interoperability, resilience and

security (Urbina et al., 2018).

This work includes an integrated approach for confidentiality and availability requirements by implementing the PRP protocol and AES. The Parallel Redundancy Protocol (PRP) defined by IEC 62439-3 standard is intended to industrial communications with high availability in Local Area Networks (LANs). Provides fault tolerance with adjustable time requirements according to specific implementation and available hardware. It resides at link layer, taking advantage of Ethernet that, among others, allows process devices to be interconnected with other devices, reducing the use of gateways that could limit real time requirements (Urbina et al., 2018). Data contained in the PRP packet, which is framed on an Ethernet frame, has vulnerabilities in networks as its load content is not authenticated nor encrypted. AES is implemented as it allows a robust and widely used confidentiality system that can be integrated along multiple sets of protocols that are currently used and in continuous evaluation according to the target application. Because of this, AES encryption is included in the Link Redundancy Entity (LRE) which is a key component of PRP end nodes. In this implementation, framing and a discard algorithm of PRP are performed based on packets formats that are proposed to include AES-CTR within its payload. For AES data encryption beyond the block size, the CTR is implemented as this mode is essential for encrypted-authenticated operations (not covered in this work), and is designed for high data rates encrypted communication.

In this context, the main objective of this work is to implement on a FPGA, the Advanced Encryption Standard (AES) and the Parallel Redundancy Protocol (PRP); and, based on IEC62439-3, evaluate the compatibility of PRP with AES for its payload confidentiality. Evaluation is made using international standard IEC62439-3 for framing correctness by comparing the PRP frame structure with an encrypted/decrypted packet transmitted from the FPGA, captured by an intermediate Ethernet Switch and decoded on Wireshark packet analyzer. Frame formats and its size restrictions are discussed. Tests for PRP performance and recovery time, as documented in IEC62438-part1, are not presented in this work due to the time cost required for development of related components. The Link Redundancy Entity (LRE) of PRP is implemented as a basic DANP or RedBox with the duplicate discard mode principle (IEC62439-3, 2016). AES IP Cores are implemented using combinational and sequential methodologies. The later is used to form an AES-CTR IP.

Physical implementation use a Xilinx® Zynq7000 FPGA-SoC (xc7z020clg484-1), embedded on a ZedBoard with an Ethernet port expansion. This device is used to report timing and utilization of IP Cores Programable Logic (PL) and, also, as the PRP RedBox cipher sender. To complete the communication scheme, a Xilinx® Kintex®-7 (xc7k325tffg676-1) FPGA integrated on a NetFPGA 1G-CML is used as the PRP RedBox decipher receiver. PRP framing

and AES control are implemented on the Processing System (PS) of the Zynq7000 (ARM) and Kintex 7 (Microblaze)

This document has the following structure: Chapter 1 presents the literature review and a context of this implementation, Chapter 2 describes the methodology using for implementing the components such as the elaboration of AES cores with Counter mode (CTR), the packets with PRP included AES for payload encryption and the algorithm that governs the operation. Chapter 3 presents the results separately for AES IP core, its Throughput, maximum frequencies and utilization showing that, to allow integration with softprocessor and other hardware components, utilization should be kept at minimum avoiding, as far as possible, decrease of throughput. Also, this chapter presents the PRP packets with its trailer and encrypted payload sent over an Ethernet network. chapter 3.5 presents the conclusions and future work regarding this implementation.

## Chapter 1

#### Literature Review

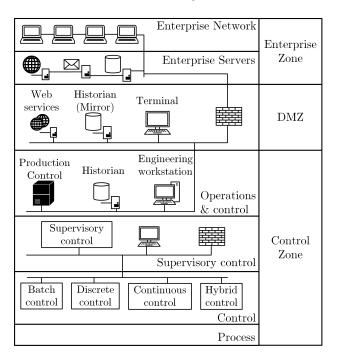

### 1.1 Industrial networks security

An industrial data network is based on models such as Computer Aided Manufacturing (CAM) and the more detailed version developed by the International Purdue Workshop on Industrial Computer Systems (Buse & Wu, 2006), adopted as an Industrial Automation and Control Systems (IACS) security standard known as ISA/IEC 62443. This model is represented in levels as shown in the Figure 1. It outlines the tasks of an integrated information management and automation system. However, the number of levels used in an industry model may vary (Buse & Wu, 2006), but each has its own policies related to physical and logical security (Knapp & Langill, 2011).

Figure 1. Reference Model for industrial control systems.

Source: Bodungen, Singer, Shbeeb, Wilhoit, and Hilt (2016).

Industrial Automation and Control Systems (IACS) have expanded from isolated networks to interconnected systems using Commercial off-the-Shelf (COTS) protocols and operating systems. IACS also are integrated with enterprise systems through different communication networks (IEC/TS62443-1-1, 2009) according to standards that allow systems to exchange

information consistently. However, this increases vulnerability to attacks and introduces potential risk in IACS with effects that include the following (IEC/TS62443-1-1, 2009):

- Unauthorized access to confidential information.

- Loss of integrity or reliability of process data and production information.

- Loss of system availability.

- Equipment damage.

- Personal injury.

- Violation of legal and regulatory requirements.

- Risk to public health and confidence.

- Threat to a nation's security.

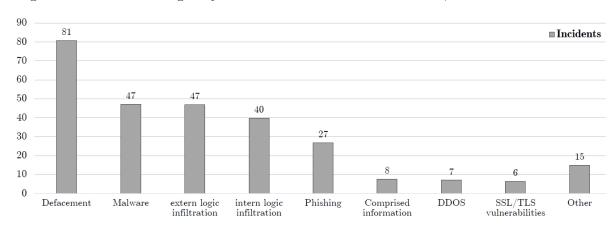

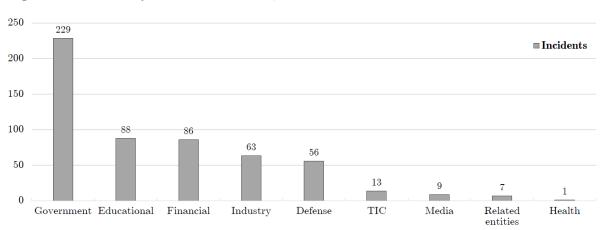

Security consultant at Red Tiger Security showed in 2010 that after testing approximately 100 North American electric power generation infrastructure, more than 38000 security warning and vulnerabilities were encountered (Knapp & Langill, 2011), and "the average number of days between the time when the vulnerability was disclosed publicly and the time when the vulnerability was discovered in a control system was 331 days" (Knapp and Langill,2011,p.32). Vulnerabilities allows sophisticated malware to be implanted on equipment, also with effects listed above and incidents with critical consequences. Several worldwide incidents can be found in Bodungen et al. (2016) and Knapp and Langill (2011). In Colombia, Comando Conjunto Cibernético (CCOC) and Colombian Computer Emergency Readiness Team (Col-CERT) worked on 769 national-defense incidents on 2014 and 957 during 2015. This later year showed that 27,4% of the incidents correspond to defacement, 16% to malware, 15,9% to logic extern infiltration and 13,5% to intern logic (Figure 2). Incidents by sectors are presented in the Figure 3.

Figure 2. Incidents managed by CCOC and ColCERT in Colombia, 2015.

Source: Conpes-3854 Consejo Política Nacional de Seguridad Digital (2016).

Figure 3. Incidents by sector in Colombia, 2015.

Source: Conpes-3854 Consejo Política Nacional de Seguridad Digital (2016).

In order to enhance security for data communications systems, public and private organizations have developed guidelines and standards which are intended to avoid incidents by means of establishing security requirements, which traditionally are focused on achieving confidentiality, integrity, and availability. Detailed requirements for security in Industrial Automation and Control Systems (IACS) are presented in Table 1. Security standards for industrial systems are shown in Appendix A.1.

Table 1. Security requirements for IACS.

| Requirement              | Description                                                                                                                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Access Control           | Control access to selected devices, information or both to protect against unauthorized interrogation of the device or information.                                                                                         |

| Use Control              | Control use of selected devices, information or both to protect against unauthorized operation of the device or use of information.                                                                                         |

| Data Integrity           | Ensure the integrity of data on selected communication channels to protect against unauthorized changes.                                                                                                                    |

| Data Confidentiality     | Ensure the confidentiality of data on selected communication channels to protect against eavesdropping.                                                                                                                     |

| Restrict Data Flow       | Restrict the flow of data on communication channels to protect against the publication of information to unauthorized sources.                                                                                              |

| Timely Response to Event | Respond to security violations by notifying the proper authority, reporting needed forensic evidence of the violation, and automatically taking timely corrective action in mission-critical or safety-critical situations. |

| Resource Availability    | Ensure the availability of all network resources to protect against denial of service attacks.                                                                                                                              |

Source: IEC IEC/TS62443-1-1 (2009).

Several protocols are standardized and documented to achieve these requirements. But as these do not have security measures included in the original standards (IEC/TS62351-1, 2007) and could be hacked by sophisticated *malware*, novel approaches are continuously developed to comply with a specific or set of requirements. Particularly, this work deals with data **confidentiality** and **availability** requirements using PRP and AES. Commercial implementations that meet high availability requirements using PRP are presented in the Table 2.

Table 2. PRP commercial devices.

| Device           | Manufacturer         | Security           |

|------------------|----------------------|--------------------|

| IE 4000          | Cisco                | IEEE802.1AE MacSec |

| IE 5000          | Cisco                | IEEE802.1AE MacSec |

| 2000U            | Cisco                | IEEE802.1AE MacSec |

| SCALANCE X204RNA | Siemens              | Not specified      |

| RED25            | Hirschmann - Blenden | Not specified      |

As seen, PRP devices do not have a security mechanism by itself. It uses protocols as MACSec to fulfill authentication and confidentiality but this is not present in all devices and limited to LAN domains which are frequently secured by obscurity, as this type of network remains on a single administration domain. Despite PRP and MACSec are constrained to LAN networks, modern transmission and distribution automation systems requires data transmission over WAN networks. These data (control, protection, supervisory) should be secured in terms of availability and confidentiality with IP support. Thus, two issues arise: availability over WAN networks using PRP and securing PRP. For the first issue, three proposals were found in (Stefanka, 2016), (Popovic, Mohiuddin, & Tomozei, 2015) and (Rentschler & Heine, 2013) but no devices nor implementations were found; for later issue, confidentiality is made based on AES with crypto engines. To propose a solution, a programable platform is mandatory. This includes hardware and software components to accelerate processes that guarantee time responses according to specifications. For this matter, Texas Instruments provides a platform based on software for developing and investigation named The Programmable Real-Time Unit Subsystem and Industrial Communication SubSystem (PRU-ICSS). But, to provide a more complex and robust programable platform that exploits both, hardware and software, FPGAs and dedicated processors are needed.

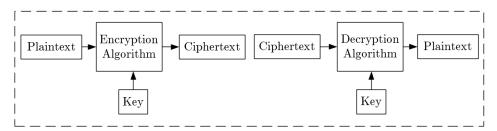

### 1.2 Cryptography

Cryptography, part of cryptology discipline, studies the techniques to create from plain text, non-comprehensible data for anyone who does not know the appropriate key. Thus, data encoded can securely be stored or transferred via any communication channel (Koscielny, Kurkowski, & Srebrny, 2013) providing confidentiality, integrity, authentication, nonrepudiation and anonymity among others (Vaudenay, 2006), depending on the encryption algorithm implemented which in general consists of the Plain text that is the data content being trans-

ferred (input); key that must remain secret for unauthorized parties (input); the process of protect the data content called encryption and the resulting encrypted message called ciphertext (Output). The encryption and decryption algorithms are assumed publicly known with private key or public-private pair keys. Both algorithms form a cipher (Koscielny et al., 2013). General components are presented in the Figure 4.

Figure 4. Cipher components.

Source: Author.

There are two types of ciphers: Symmetric and Asymmetric. The first use duplicate Keys for encryption and decryption while second, also referred as public-key ciphers, use a different pair of keys for each algorithm named public and private keys. "The first of them is publicly available. Everybody can use it to encrypt messages. But only the corresponding private key allows decryption. Thus the only person able to run decryption is the one who has the private key" (Koscielny et al., 2013).

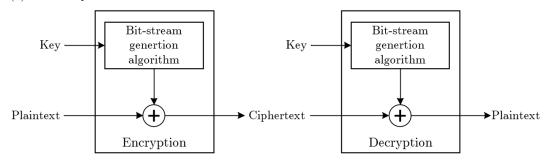

#### 1.2.1 Symmetric algorithms

"Symmetric algorithms are fast and are used for encrypting - decrypting high volume data" (Rodriguez-Henriquez, Saqib, Pérez, & Koc, 2006), encode Plaintext by **stream** (Figure 5a) when one of its bits or bytes is processed by the algorithm at a time, or by **block** (Figure 5b) when a set of bytes are processed producing an output block of equal length. "Typically, a block size of 64 or 128 bits is used" (Stallings, 2013). Block ciphers "seem applicable to a broader range of applications than stream ciphers. The vast majority of network-based symmetric cryptographic applications make use of block ciphers" (Stallings, 2013). In the Table 3, examples of stream and block ciphers are shown.

Table 3. Stream and block ciphers.

| Symmetric type | Algoritmhs                                                                                                                                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stream ciphers | Vigenère, Vernam, SEAL, TWOPRIME, WAKE, RC4, A5                                                                                                                |

| Block ciphers  | DES, AES Rijndael, Serpent, RC5, RC6, MARS, IDEA, Twofish, Blowfish, CAST, FEAL, GOST, TEA, SAFER k64, Twofish, DEAL, LOKI97, LOKI91, MISTY, MMB, Madryga, ICE |

Figure 5. Stream cipher and Block cipher.

#### (a) Stream cipher.

#### (b) Block cipher.

Source: Stallings (2013).

One of the most popular symmetric block cipher is the Data Encryption Standard (DES). "In 1973 the US National Bureau of Standards (NBS) solicited proposals for a uniform and reliable encryption algorithm that could be applied, among other places, in commercial communication systems" (Koscielny et al., 2013). The algorithm developed at IBM by Horst Feistel and Dan Coppersmith in 1974 was accepted and became widely deployed in many applications despite its 56-bit key length that nowadays can be discovered in hours by a brute force attack

(Rodriguez-Henriquez et al., 2006). Because this vulnerability, a variation of DES called Triple-DES or 3DES that uses three 56-bit keys and may offer a security of a 112-bit key is widely used (Rodriguez-Henriquez et al., 2006). But DES is destined to be replaced by the Advanced Encryption Standard (AES) in order to improve confidentiality.

## 1.2.2 AES and the Rijndael Algorithm

Rijndael algorithm, developed by Joan Daemen and Vincent Rijmen, became the Advanced Encryption Standard (AES) in November 2001 after a selection process initiated in January 1997 by the National Institue of Standards and Technology (NIST). AES is a byte-oriented symmetric block cipher that requires 10, 12 or 14 rounds of encryption for key sizes of 128, 192 or 256 bits respectively, operating as a classic substitution/permutation relying on operations in the field  $GF(2^8)$  (Dobbertin, Rijmen, & Sowa, 2005). AES is composed with an input block, four transformation modules, a key generator and an output block. The **input block** is a 128 bit-lenght of plain data, arranged in a matrix as described in the Figure 6, where each column forms a 4 byte word called  $N_b$ -word.

Figure 6. AES input block to cipher.

| $a_0$ | $a_4$ | $a_8$    | $a_{12}$ |

|-------|-------|----------|----------|

| $a_1$ | $a_5$ | $a_9$    | $a_{13}$ |

| $a_2$ | $a_6$ | $a_{10}$ | $a_{14}$ |

| $a_3$ | $a_7$ | $a_{11}$ | $a_{15}$ |

source: Dobbertin et al. (2005)

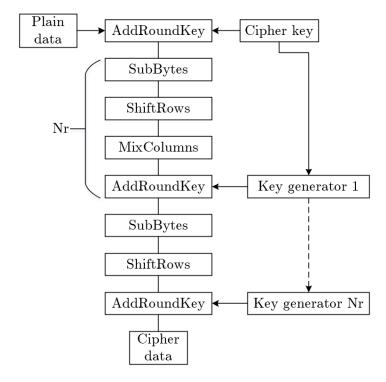

Transformation modules, named SubBytes, ShiftRows, MixColumns and AddRoundKey (NIST, 2001a) form a round of the cipher with some variations at start and end rounds. The key-expansion module or **key generator**, generates a key per round until completion of the encryption process. Figure 7 presents the AES parts integrated, where  $N_r$  is the number of rounds modules should be repeated according to the cipher-key being used, which is arranged in a matrix where each column is 32-bit length with  $N_k$  columns.

Figure 7. AES cipher.

Source: Author.

The relation between the number of rounds  $N_r$  and the key size  $N_k$  is shown in the Table 4.

Table 4. Key-Block-Round Combinations.

| Name    | Key length $(N_k \text{ words})$ | Block size $(N_b \text{ words})$ | Number of rounds $(N_r)$ |

|---------|----------------------------------|----------------------------------|--------------------------|

| AES-128 | 4                                | 4                                | 10                       |

| AES-192 | 6                                | 4                                | 12                       |

| AES-256 | 8                                | 4                                | 14                       |

Source: IEC - IEC/TS62443-1-1 (2009).

Detailed AES components and operations are presented in NIST (2001a) and Daemen and Rijmen (2002). AES encryption is currently active and presents a usable time estimation of years ahead as defined by NIST and seen in the Table 5.

Table 5. Approval Status of Symmetric Algorithms Used for Encryption and Decryption.

| Algorithm | Use        |

|-----------|------------|

| AES-128   | Acceptable |

| AES-192   | Acceptable |

| AES-256   | Acceptable |

Source: SP800131A (2015).

Besides, AES uses the three key lengths that are also acceptable by National Institue of Standards and Technology (NIST) and widely deployable. Table 6 shows the recommendation for key management.

Table 6. Recommendation for key management.

| Security<br>Strength | Through 2030 | 2031 and Beyond |

|----------------------|--------------|-----------------|

| 128                  | Acceptable   | Acceptable      |

| 192                  | Acceptable   | Acceptable      |

| 256                  | Acceptable   | Acceptable      |

Source: SP80057Part1 (2016).

#### 1.2.3 Modes of operation

Modes of operation allows block ciphers to encrypt data that must cope beyond the block size. For example, AES block size is 128 bit, so to encrypt data grater than 128 bits, is necessary to partition it in blocks of the same size. But if these partitioned blocks use the same key, security vulnerabilities increase (Stallings, 2013), so a mode of operation is required to enhance security of a cryptography algorithm. Modes of operation are divided according to the application. Seven parts are defined by the NIST and presented in the Table 7.

Table 7. Block cipher's Modes of operation.

| Part | service                                        | Name                                                                     | Standard                       |

|------|------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|

| 1    | Confidentiality                                | Electronic CodeBook mode (ECB)                                           | SP800-38A                      |

|      |                                                | Chiper Block Chaining mode (CBC)                                         |                                |

|      |                                                | Chiper Feedback mode (CFB)                                               |                                |

|      |                                                | Output Feedback mode (OFB)                                               |                                |

|      |                                                | Counter mode (CTR)                                                       |                                |

| 2    | Authentication                                 | cipher-based message authentication code (CMAC)                          | SP800-38B                      |

| 3    | Authentication<br>Confidentiality              | Counter with Cipher Block Chaining-<br>Message Authentication Code (CCM) | SP800-38C                      |

| 4    | High-Throughput Authentication confidentiality | Galois/Counter Mode (GCM)                                                | SP800-38D                      |

| 5    | Storage Confidentiality                        | XEX Tweakable Block Cipher with Ciphertext Stealing (XTS) (XTS-AES)      | SP800-38E<br>IEEE1619-<br>2007 |

| 6    | Key Wrapping                                   | Key Wrap (KW)                                                            | SP800-38F                      |

|      |                                                | Key Wrap Padding (KWP)                                                   |                                |

| 7    | Format- Preserving Encryption                  | format-preserving, Feistel-based encryption (FF1)                        | SP800-38G                      |

As this work attempts to provide a confidentiality -and redundancy- mechanism for data transmissions, part 1 is considered for implementation process, specifically, the Counter mode (CTR) mode as this best fits the requirements and is scalable in a way that can be used for other modes of operation as Galois/Counter Mode (GCM) or Counter with Cipher Block Chaining-Message Authentication Code (CCM). In Table 8, a description of the modes of operation related strictly to confidentiality are shown.

Table 8. Modes of operation Part 1 description.

| Mode                                | Description                                                                                                                                                                                                                     | Typical application                                                 |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| Electronic Code-<br>Book mode (ECB) | Input data (plain text) of blocks are encoded separately using the same key.  Transmission of unique as an encryption key                                                                                                       |                                                                     |  |

| Chiper Block Chaining mode (CBC)    | Input data (plaintext) is the xor of the plain data of the next block and the previous block output data(cipher text).                                                                                                          |                                                                     |  |

| Chiper Feedback<br>mode (CFB)       | Input data is processed a set of bits at once. Output data of previous block, is passed as input to the cipher to generate pseudorandom output data. This is xored with the input data to produce subsequent set of ciphertext. | Stream-oriented communication and authentication.                   |  |

| Output Feedback mode (OFB)          | Like CFB, except that the input data is<br>the preceding cipher output. Uses all<br>available blocks.                                                                                                                           | Stream-oriented communication.                                      |  |

| Counter mode (CTR)                  | Blocks of input data are xored independently with a ciphered counter. For each next block, the counter is incremented.                                                                                                          | Block-oriented transmission<br>Used for high speed require<br>ments |  |

Source: Stallings (2013).

Currently, new proposals are being presented for authentication and encryption in the Competition for Authenticated Encryption: Security, Applicability, and Robustnes (CAESAR). These proposals aim to improve AES-GCM performance for lightweight devices and include both, block and stream ciphers. Detailed information and implementation is beyond the scope of this work, but can be found in (Farzaneh Abed, 2016) and in the International-Cryptologic-Research-Community (2017).

## 1.3 Redundancy in communication networks

In order to accomplish high availability in networks, a redundancy scheme is implemented according to specific application requirements such as topology, recovery time, data-packet losses and devices involved in the redundancy process. Applications such as enterprise networks are considered non-critical for recovery time and packet losses at network layer or lower.

For automation networks, requirements meet enhanced performance. See Table 9.

Table 9. grace time per application examples.

| Applications             | Typical grace time (s) |

|--------------------------|------------------------|

| Uncritical automation    | 20                     |

| Automation management    | 2                      |

| General automation       | 0.2                    |

| Time-critical automation | 0.020                  |

Source: IEC62439-1 (2013).

Redundancy can be dynamic or static. On dynamic redundancy, devices react to failures within the network. On the other hand, static redundancy acts in a parallel manner as devices are active concurrently. In the Table 10, a list o protocols for redundancy are shown.

Table 10. Examples of redundancy protocols.

| Protocol | Solution       | Frame loss | Redundanc<br>Protocol | yEnd<br>node<br>attach-<br>ment | Network<br>topology | Recovery<br>time                        |

|----------|----------------|------------|-----------------------|---------------------------------|---------------------|-----------------------------------------|

| IP       | IP routing     | Yes        | Within the network    | Single                          | Single<br>meshed    | > 30s typical<br>not determin-<br>istic |

| STP      | IEEE<br>802.1D | Yes        | Within the network    | Single                          | Single<br>meshed    | > 20s typical<br>not determin-<br>istic |

| RSTP     | IEEE<br>802.1D | Yes        | Within the network    | Single                          | Single meshed, ring | Can be deterministic                    |

Source: IEC62439-1 (2013).

Table 10. (Continued) Examples of redundancy protocols.

| Protocol | Solution        | Frame loss | Redundanc<br>Protocol | yEnd<br>node<br>attach-<br>ment | Network<br>topology           | Recovery<br>time                                                                         |

|----------|-----------------|------------|-----------------------|---------------------------------|-------------------------------|------------------------------------------------------------------------------------------|

| CRP      | IEC 62439-<br>4 | Yes        | In the end nodes      | Single<br>and dou-<br>ble       | Doubly meshed, crossconnected | 1s worst case<br>for 512 end<br>nodes                                                    |

| DRP      | IEC 62439-      | Yes        | Within the network    | Single<br>and dou-<br>ble       | Ring, double ring             | 100 ms worst<br>case for 50<br>switches                                                  |

| MRP      | IEC 62439-<br>2 | Yes        | In the end nodes      | Single                          | Ring                          | 500 ms, 200 ms, 30 ms or 10 ms worst case for 50 switches depending on the parameter set |

| BRP      | IEC 62439-<br>5 | Yes        | In the end nodes      | Double                          | Doubly meshed, connected      | 4,8 ms worst case for 500 end nodes                                                      |

| PRP      | IEC 62439-<br>3 | No         | In the end nodes      | Double                          | Doubly meshed, independent    | 0s                                                                                       |

| HSR      | IEC 62439-      | No         | In the end nodes      | Double                          | Ring,<br>meshed               | 0s                                                                                       |

Source: IEC62439-1 (2013).

## 1.3.1 The Parallel Redundancy Protocol - PRP

The Parallel Redundancy Protocol (PRP) is defined in the Section 4 of the IEC62439-3 (2016) standard for high availability in automation networks. PRP is implemented in end nodes,

avoids frame losses and guarantees seamless recovery time (IEC62439-1, 2013). PRP allows high availability services by duplicating a packet and sending it over two independent LAN networks to only one destination at a time. Provides redundancy in end devices rather than in network components using nodes called DANPs (IEC62439-3, 2016). Thus, source DANP sends two frames in a parallel manner to a destination DANP that receives those frames in a time lapse depending on the two LAN topologies involved, passing the Link Service Data Unit (LSDU) contained in the first received frame to upper layers and discarding the second frame. LANs attached to a DANP must be identical in the suite of protocols at the Logical Link Control (LLC) data-link sublayer, specifically IEEE802.3 and IEEE802.1D, to accomplish the resilience specified by IEC62439-1 (2013), but each LAN can be different in topology and performance (IEC62439-3, 2016). These LANs named LAN A and LAN B (as the standard call them), should operate simultaneously and be "fail-independent". Figure 8 presents a PRP network with the elements that compose it such as: end nodes like SANs, RedBox and DANPs; elements within the LANs like IEEE802.1D bridges, edge ports, inter-switch ports and inter-switch links; and the leaf-links between LANs and end nodes. Particularly, DANP and RedBox nodes need a Link Redundancy Entity (LRE) in their protocol stack for adequate operation of PRP.

source Leaf Link DANP B-frame DANP inter-switch Link SAN A-frame **A**1 bridge bridge bridged local area bridged local area Inter-switch ports network (ring) network (tree) LAN\_B LAN\_A bridge bridge bridge bridge <del>annin</del> <del>mim</del> шіпп Leaf Links SAN SAN SAN A2 RedBox B2 A-frame B-frame SAN SAN DANP Edge ports DANP DANP destination

Figure 8. PRP Redundancy Network.

Source: IEC62439-3 (2016).

### 1.3.1.1 Link Redundancy Entity - LRE

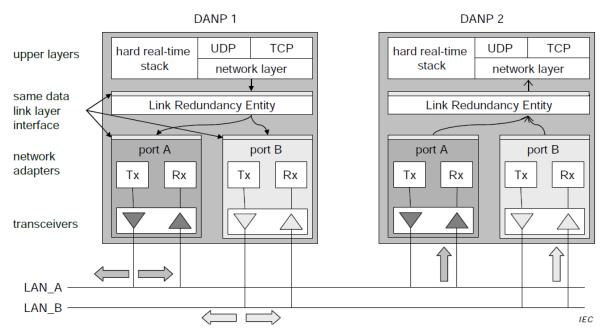

End nodes have a single connection as the SAN node or more than one as the DANP and RedBox nodes. These later nodes require a Link Redundancy Entity (LRE) in their link layer to hide redundancy from upper layers (IEC62439-1, 2013) and operate ports in parallel. LRE in DANP nodes interfaces two ports with one upper layer stack (Figure 9). It handles duplicated frames and redundancy management (IEC62439-3, 2016).

Figure 9. PRP with two DANP.

Source: IEC62439-3 (2016).

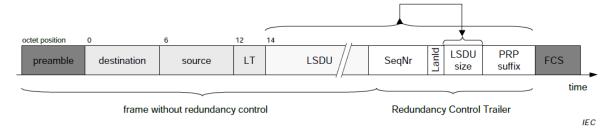

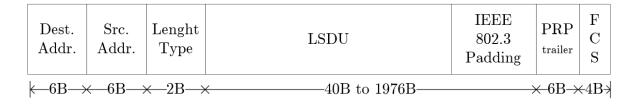

When sending data at the link layer, the LRE inserts six bytes called Redundancy Control Trailer (RCT) between the Ethernet Frame Check Sequence (FCS) and LSDU (Figure 10). Considerations for tagged and padded frames are also considered by the IEC62439-3 (2016). A IEEE802.1Q tagged frame is modified like regular Ethernet frames with the RCT, but padded frames, when required should be filled before adding the RCT, thus avoid scanning it twice (IEC62439-3, 2016). RCT has four fields that allows redundancy to be achieved using PRP. These are shown in the Table 11.

Figure 10. PRP with RCT.

Source: IEC62439-3 (2016).

Table 11. Redundancy Control Trailer (RCT) fields.

| Field     | Length (bit) | Name              |

|-----------|--------------|-------------------|

| SeqNr     | 16           | Sequence Number   |

| LanId     | 4            | LAN Identifier    |

| LanId     | 4            | LAN Identifier    |

| PRPsuffix | 16           | PRP suffix at RCT |

"Sequence Number (SeqNr) is incremented for each frame a DANP sends. The doublet source MAC address, sequence number uniquely identifies copies of the same frame"IEC62439-3 (2016). The LAN Identifier (LanId) field allows a receiver to know which LAN the frame is received from. LAN'A, has the value 1010 (xA) and LAN'B 1011 (xB). when receiving a LanId different than expected an error is noticed with monitoring purposes.

## 1.4 NetFPGA and ZedBoard

Some features provided by the ZedBoard and NetFPGA are listed in Table 12.

Table 12. Zedboard and NetFPGA features.

| Feature | NetFPGA                                                             | ZedBoard                                              |  |  |

|---------|---------------------------------------------------------------------|-------------------------------------------------------|--|--|

|         | Xilinx <sup>®</sup> Kintex <sup>®</sup> -7 XC7K325T-1FFG676<br>FPGA | Xilinx <sup>®</sup> XC7Z020-1CLG484C Zynq-7000 AP SoC |  |  |

| Memory  | X16 4.5 MB QDRII+ static RAM (450 MHz)                              | 512 MB DDR3 (128M x 32)                               |  |  |

Table 12. (Continued) Zedboard and NetFPGA features.

| Feature    | NetFPGA                                                      | ZedBoard                                       |

|------------|--------------------------------------------------------------|------------------------------------------------|

|            | X8 512 MB DDR3 dynamic RAM (800 MHz)                         | 256 Mb QSPI Flash                              |

|            | 1-Gbit BPI Flash                                             |                                                |

| Interfaces | SD card slot                                                 | SD Card                                        |

|            | Four 10/100/1000 Ethernet PHYs with RGMII                    | 10/100/1G Ethernet                             |

|            | X4 Gen 2 PCI Express                                         | USB 2.0 FS USB-UART bridge                     |

|            | FMC connector                                                | LPC FMC connector                              |

|            | Two Pmod ports                                               | USB-JTAG Programming                           |

| Oscillator | 200 MHz                                                      | 100 MHz (PL)                                   |

|            |                                                              | 33.333 MHz (PS)                                |

| Other      | 32-bit PIC microcontroller                                   | HDMI Output                                    |

|            | USB microcontroller                                          | VGA (12-bit Color)                             |

|            | Real time clock                                              | 128x32 OLED Display                            |

|            | Crypto-authentication chip                                   | Audio Line-in, Line-out, headphone, microphone |

|            | Four on-board LEDs and four on-board general-purpose buttons | Two Reset Buttons                              |

|            |                                                              | Seven Push Buttons                             |

|            |                                                              | Eight dip/slide switches                       |

|            |                                                              | Nine User LEDs                                 |

Detailed information can be found on the "NetFPGA-1G-CML" Board Reference Manual" Digilent (2016) and "Zynq" Evaluation and Development Hardware User's Guide" Xilinx (2014).

## Chapter 2

## Methodological Design of the Implementation

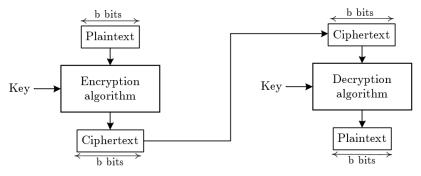

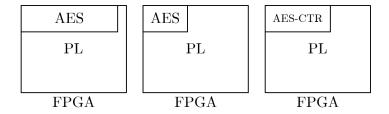

To implement confidentiality and high-availability over a Gigabit Ethernet (GigaE) environment, the Parallel Redundancy Protocol (PRP) and Advanced Encryption Standard (AES) with Counter mode (CTR) of operation are selected. First, AES with CTR blocks are designed. AES, based in standard (SP800131A, 2015), is designed using combinational and sequential-combinational methods separately and implemented on the Programable Logic (PL) of the FPGA. Then, Counter mode (CTR) is added as documented in (NIST, 2001a). These blocks are presented in the Figure 11.

Figure 11. Blocks of AES combinational (left), sequential (center) and sequential AES with CTR (right).

Source: Author.

Sequential design method, as found in the documentation available for AES on FPGA, can be divided in pipelined and non-pipelined. This work shows the non-pipelined implementation for the Sequential method. AES and CTR performance are measured in terms of FPGA utilization and timing using Vivado's Synthesis and implementation as presented in chapter 3. For pipelined designs, higher utilization and throughput are expected compared to the same parameters on non-pipelined designs. Thus, the later uses lower FPGA area utilization with the disadvantage of limited throughput (in the order of Giga-bits per seconds), while pipelined throughput achieves tens or hundreds of Giga-bits per second (Silitonga, Jiang, Khan, & Becker, 2019). Chapter 3 presents a comparative of implementations based on similar devices as those used here and the reports for timing and utilization.

Framing and operation related to the Parallel Redundancy Protocol (PRP) are then designed based in standard (IEC62439-1, 2013). Its integration with AES-CTR is made by taking the encrypted data and place it within a PRP packet. Two pair of packets are proposed, the first transmits plain PRP parameters and an encrypted Link Service Data Unit (LSDU). For the second pair of packets, PRP parameters and LSDU are encrypted.

Operation for transmission and reception of encrypted PRP packets are designed to be implemented on the Processing System (PS) of the SoC-FPGA or soft-processor on the FPGA.

The described components and PRP related elements (subsection 1.3.1) are presented in the Figure 12.

Figure 12. System block components.

Source: Author.

To verify the operation of the implemented modules and interconnections, specifically, to verify encryption and redundancy, packets are sent between the Non-redundant networks and analyzed in the redundant network. The following sections show these components design in detail.

## 2.1 AES combinational and non-pipelined (sequential) design

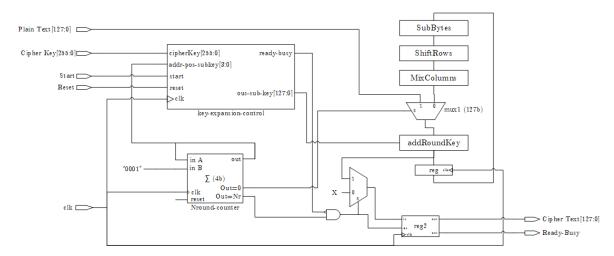

Cipher and its inverse design are based on the transformations specified in NIST named (inv)SubBytes, (inv)ShiftRows, (inv)MixColumns and (inv)AddRoundKey. Both with the same Key Expansion. Pure combinational blocks are represented in the Figure 13.

Figure 13. AES Cipher and inverse cipher combinational blocks.

Source: Author.

Unlike combinational method which only requires connections of combinational-elements, se-

quential strategy presents more timing complexity, thus requiring deeper design considerations as described in the Figure 15 for the system process blocks and Figure 14 for state machine.

Figure 14. Process blocks state machine.

Source: Author.

The encryption process of sequential AES is straight forward. For each cycle SubBytes, ShiftRows, MixColumns and AddRoundKey are performed, and, Key generation is done once every cycle. The quantity of cycles depends on the key being used. Despite NIST (2001a) defines 10, 12 and 14 cycles for 128, 192 and 256 bit-length keys respectively, this work results (Chapter 3) requires an extra cycle in order to load data on the encryption core. The block diagram is presented in the Figure 15.

Figure 15. AES process blocks.

Inverse sequential AES requires that the key generation encounters all subkey to start backwards. As a result, all subkeys are first generated and stored in a custom RAM memory. Once the key generation process is finished, the inverse cipher submodules start. Figure 16 presents its block diagram.

Figure 16. Inverse AES process blocks.

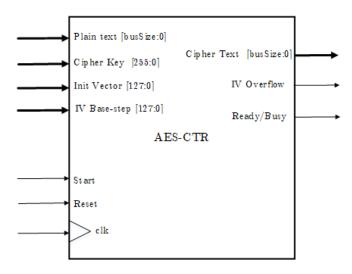

Sequential method requires three additional inputs to control the AES process. These are the *clock* signal, *start* and *reset* ports. Also it has an extra output that allows monitoring of process completion, this is named *Ready/Busy*. These are represented in the Figure 17.

Cipher Text [128:0]

Cipher Key [255:0]

Start AES (cipher)

Reset Ready/Busy

Cipher Text [128:0]

Plain text [128:0]

Plain text [128:0]

Cipher Key [255:0]

Start AES (inv. cipher)

Reset Ready/Busy

Figure 17. AES Cipher and inverse cipher Sequential-combinational blocks.

Source: Author.

After AES design, the CTR mode of operation is included into sequential AES. Combinational AES is excluded for CTR operation due to its high utilization and the fact that the implemented design requires four AES blocks.

# 2.2 AES (sequential) integrated blocks for CTR

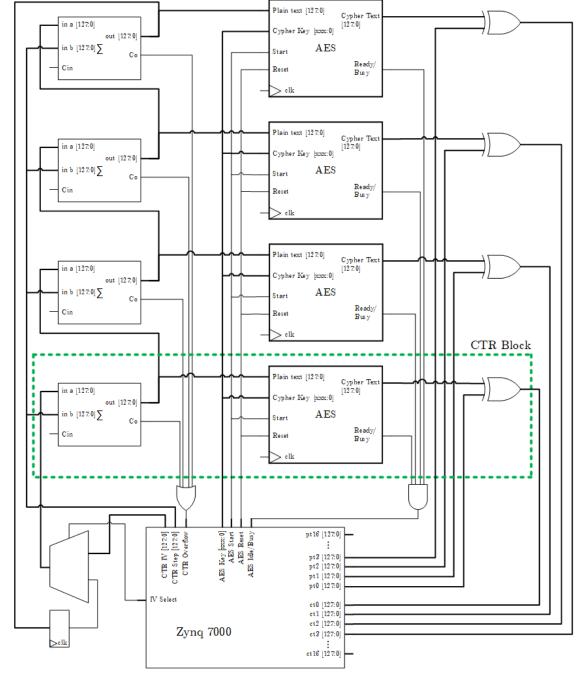

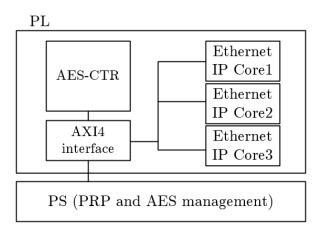

According to the properties of CTR mode of operation, the cipher block is applied for encryption and decryption, thus, sequential AES-128 is grouped with a counter to form a CTR Block. Four blocks are connected in parallel and its inputs and outputs are connected to the processing system as seen in the Figure 18.

Figure 18. AES-CTR, Ethernet and processing system block diagram.

IP Core design for AES-128-CTR is presented in the Figure 19.

Figure 19. AES-CTR, block diagram.

## 2.3 PRP framing and algorithm

PRP implementation is performed entirely at Processing System (PS) for framing and discarding algorithm. Supervisory frames are not included in this work. Based on the following frame packet, formats are proposed to extend this implementation for further integration with key exchanges and VLANs. First PRP trailer gets incorporated into the IEEE802.3 frame with its documented minimum and maximum LSDU sizes. This is shown in the Figure 20. The PRP trailer is implemented according to its structure and bit sizes as described in the Figure 21.

Figure 20. Ethernet frame with PRP trailer.

Source: Author.

PRP trailer description and sizes are presented in the Figure 21, where SeqNr is the sequence number of each redundant packet, LanID is the LAN identification that can be LANA or LANB, and, the LSDU size with the PRP suffix are used to validate a valid PRP trailer.

Figure 21. PRP trailer details.

| SeqNr                                                              | LanID | LSDU size | PRP<br>suffix |  |  |  |  |

|--------------------------------------------------------------------|-------|-----------|---------------|--|--|--|--|

| $\leftarrow$ 16b $\rightarrow$ 12b $\rightarrow$ 16b $\rightarrow$ |       |           |               |  |  |  |  |

PRP Link Redundancy Entity (LRE) capabilities for this work, are designed based on the diagram flow presented in the Figure 22.

Figure 22. PRP LRE Flow diagram on the Processing System (PS).

# 2.4 PRP and AES-CTR integration design

Integration of AES-CTR with PRP is designed based on its packet structure. The Figure 23 presents the design for the frame with encrypted payload. This do not interfere with Ethernet header nor PRP trailer.

Figure 23. Ethernet frame with encrypted LSDU and plain PRP trailer.

| Dest.<br>Addr.                                                                                                               | Src.<br>Addr. | Lenght<br>Type | AES Encrypted t |  | F<br>C<br>S |  |

|------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-----------------|--|-------------|--|

| $\leftarrow$ 6B $\rightarrow$ 6B $\rightarrow$ 2B $\rightarrow$ 40B to 1976B $\rightarrow$ 4B $\rightarrow$ 4B $\rightarrow$ |               |                |                 |  |             |  |

Source: Author.

The Figure 24 shows the design and lengths of an Ethernet frame with the IEEE802.1Q tag and the PRP trailer.

Figure 24. Ethernet with VLAN tag and encrypted LSDU and plain PRP trailer.

| Dest.<br>Addr.                                                                           | Src.<br>Addr. | IEEE<br>802.1Q<br>Tag | Lenght<br>Type | AES Encrypted | PRP<br>trailer | F<br>C<br>S |

|------------------------------------------------------------------------------------------|---------------|-----------------------|----------------|---------------|----------------|-------------|

| $k$ 6B $\times$ 6B $\times$ 4B $\times$ 2B $\times$ 36B to 1972B $\times$ 6B $\times$ 4B |               |                       |                |               |                |             |

Source: Author.

As an alternative, the PRP trailer is encrypted to hide redundancy information, but this implies to generate a PRP secure tag which allows the receiver node to multiplex and decipher at Data-link layer. The Figure 25 presents the design for this packet with its bit sizes.

Figure 25. Ethernet frame with encrypted LSDU and PRP trailer.

| Dest.<br>Addr.                                                            | Src.<br>Addr. | PRP<br>Secure<br>Tag | Lenght<br>Type | AES Encrypted | F<br>C<br>S |

|---------------------------------------------------------------------------|---------------|----------------------|----------------|---------------|-------------|

| $k$ 6B $\times$ 6B $\times$ 4B $\times$ 2B $\times$ 42B to 1978B $\times$ |               |                      |                |               |             |

The Figure 26 shows the same scenario of encrypted PRP trailer and PRP secure tag for multiplexing with the addition of the IEEE802.1Q tag for VLANs.

Figure 26. Ethernet and VLAN tag frame with encrypted LSDU and PRP trailer.

| Dest.<br>Addr.                                                                                | Src.<br>Addr. | IEEE<br>802.1Q<br>Tag | PRP<br>Secure<br>Tag | Lenght<br>Type | AES Encrypted | F<br>C<br>S |  |

|-----------------------------------------------------------------------------------------------|---------------|-----------------------|----------------------|----------------|---------------|-------------|--|

| $\leftarrow$ 6B $\rightarrow$ 4B $\rightarrow$ 4B $\rightarrow$ 38B to 1974B $\rightarrow$ 48 |               |                       |                      |                |               |             |  |

Source: Author.

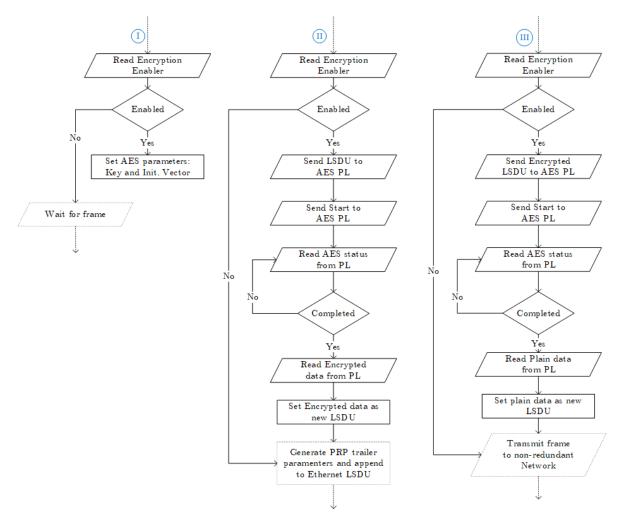

Once integrated in the packet, AES is controlled from PRP Link Redundancy Entity (LRE) by adding the corresponding code described in the Figure 27 and connected to previously LRE flow (Figure 22).

Figure 27. PRP with AES integration flow diagram on the Processing System (PS).

Hardware integration of PRP and AES-CTR is elaborated by the interconnection of Programable Logic (PL) elements with the Processing System (PS). This interconnection is made by using the Advanced eXtensible Interface (AXI) interface, which permits the communication between the Ethernet interfaces and the AES-CTR Cores, with the Processing System. The Figure 28 shows the diagram with the elements required.

Figure 28. PRP with AES-CTR Hardware integration.

## 2.5 PRP and AES-CTR integration verification

To verify operation of the system, two devices are required (Figure 12). Each device is described previously Figure 28, where the Ethernet Cores are used to connect to the redundant and non-redundant networks.

Two tests are identified to verify and evaluate the implementation: a simple communication to verify correctness of PRP framing and its encrypted payload using different packet sizes; and, a Unit Under Test (UUT) methodology to evaluate the performance of the complete system. In the simple communication scheme (Figure 29), a packet is sent from the non-redundant network and received in the device (step 2 in the figure), then, (step 3) this device send the packets with their PRP trailers and ciphered LSDU to the redundant network by using parts of the operation flow as described in the Figure 22 and Figure 27. At step 4, the device apply the discarding algorithm (Figure 22 and Figure 27), decipher the payload (LSDU) and send to the non-redundant network (Step 5).

Figure 29. PRP with AES-CTR simple communication verification.

This communication verification is used in this work, and its results are shown in Chapter 3. On the other hand, the UUT scheme (Figure 30) let the performance parameters of the integrated system be evaluated on physical implementation. The parameters that can be physically tested (including PL and PS), among others, are the throughput, transmission rates and packet losses.

Figure 30. PRP with AES-CTR UUT test.

Source: Author.

The UUT test requires a packet generator and analyzer, which transmits an specific packet data and expects to receive the same packet on its other interface to compare quantity of transmitted packets versus received, latency and loss rate, among others. Although the benefits of the UUT test, this is not presented in this work considering availability of the packet analyzer, the time extension required to develop the current work and the enhancements identified for the AES-CTR Core. These considerations are left for future work and explained in the section 3.5.

## Chapter 3

## Results and Analysis

The physical implementation use a Xilinx® Kintex®-7 XC7K325T Net-FPGA and Xilinx® Zedboard with FMC ports. Those physical components are named DANP-RedBox. Zedboard implements DANP-RedBox-1 for cipher and to send to PRP redundant network. On the other hand, NetFPGA implements DANP-RedBox-2 to decryption process and PRP-LRE discarding algorithm.